- 您现在的位置:买卖IC网 > Sheet目录1249 > TS-MAC-XM-UT4 (Lattice Semiconductor Corporation)SITE LICENSE ETH MAC TRI-SPD XP

�� �

�

Lattice� Semiconductor�

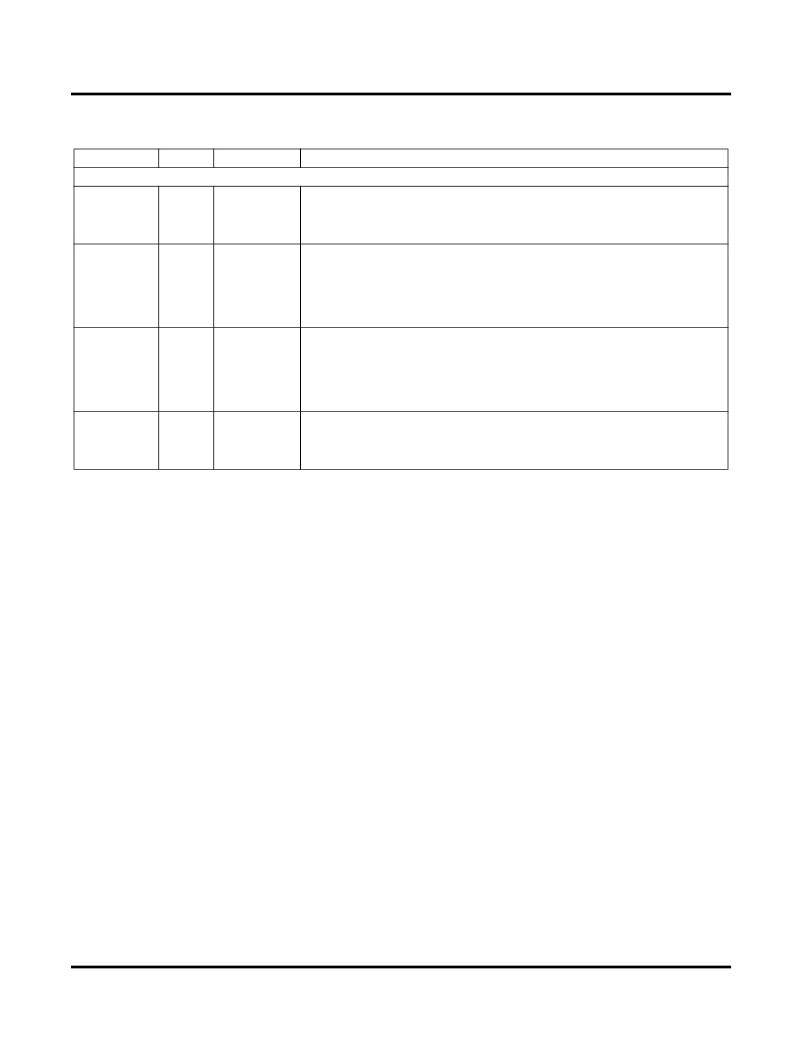

�Table� 2-2� lists� TSMAC� IP� core� system� input� and� output� signals.�

�Table� 2-2.� TSMAC� IP� Core� System� Input� and� Output� Signals�

�Functional� Description�

�Port� Name�

�Type�

�Active� State�

�Description�

�Clocks� and� Reset�

�System� Clock� .� In� the� 1G� mode,� the� Tx� MAC� is� clocked� by� this� signal.� All� the� input�

�sys_clk�

�Input�

�N/A�

�and� the� output� signals� of� the� Tx� MAC� are� synchronous� to� this� clock� in� the� 1G�

�mode.� The� frequency� is� always� at� 125� MHz.� Note� in� the� 1G� mode� the� core’s�

�txmac_clk� is� derived� from� this� clock.�

�Transmit� Clock� .� This� clock� is� used� in� the� 10/100� Mbps� mode� only.� The� Tx� MAC,�

�Tx� MAC� application� interface� and� the� MII� are� synchronous� to� this� signal.� This�

�tx_clk�

�Input�

�N/A�

�clock� has� a� frequency� of� 2.5/25� MHz� for� 10/100� Mbps� operation� respectively.� Note�

�in� the� 10/100� mode� tx_clk� is� divided� by� two� to� provide� the� clock� (txmac_clk)� to� the�

�transmit� MAC� section.� In� the� 10/100� mode� the� transmit� signals� at� the� GMII� inter-�

�face� are� always� synchronous� to� tx_clk.�

�Receive� Clock� .� This� clock� is� an� input� from� the� PHY� device.� In� the� 1G� mode,�

�rx_clk� frequency� is� 125� MHz� while� in� the� 10/100� mode,� the� corresponding� rx_clk�

�rx_clk�

�Input�

�N/A�

�frequency� is� 2.5/25� MHz� respectively.� In� the� 10/100� mode� rx_clk� is� divided� by� two�

�to� provide� the� clock� (rxmac_clk)� to� the� Receive� MAC� section.� In� the� 1G� mode� this�

�clock� is� provided� directly� to� the� Receive� MAC� section.� The� receive� signals� at� the�

�GMII� interface� are� always� synchronous� to� rx_clk.�

�Gigabit� Transmit� Clock� .� This� clock� is� used� in� the� 1G� mode� only.� The� transmit�

�gtx_clk�

�Output�

�N/A�

�signals� that� are� outputs� on� the� GMII� interface� are� synchronous� to� this� clock.� This�

�clock� has� a� frequency� of� 125� MHz.� This� clock� is� derived� from� the� sys_clk.� See�

�Figure� 2-6� .�

�Host� Interface�

�The� Host� Interface� module� is� a� fully� synchronous� module� that� runs� off� the� host� clock.� A� number� of� registers� are� ini-�

�tialized� via� the� Host� interface� to� ensure� that� the� TSMAC� IP� core� functions� as� intended.� The� write� operation� to� an�

�internal� register� is� initiated� when� the� hcs_n� and� hwrite_n� signals� are� asserted� and� hread_n� signal� is� deasserted.�

�The� address� of� the� targeted� register� is� placed� on� the� haddr� bus,� while� the� valid� data� is� placed� on� the� hdatain� bus.�

�The� contents� of� the� address� and� data� busses� should� remain� unchanged� until� the� TSMAC� IP� core� asserts� the�

�hready_n� signal.� The� signals� hcs_n,� hwrite_n� and� hread_n� must� remain� unchanged� until� hready_n� is� asserted.�

�A� register� read� is� initiated� by� asserting� the� hcs_n� and� hread_n� signals,� while� keeping� the� hwrite_n� signal� deas-�

�serted.� The� address� of� the� targeted� register� is� placed� on� the� haddr� bus.� The� TSMAC� IP� core� places� the� content� of�

�the� targeted� register� on� the� hdataout� bus� and� qualifies� it� with� the� assertion� of� hready_n� signal.� The� haddr� bus�

�should� not� change� until� the� hready_n� signal� is� asserted.�

�Figure� 2-17� shows� the� timing� diagram� associated� with� the� host� interface� write� and� read� operations.�

�Receive� MAC� (Rx� MAC)�

�The� main� function� of� the� Rx� MAC� is� to� accept� the� formatted� data� from� the� G/MII� interface� and� pass� it� to� the� host�

�application� through� an� external� FIFO.� In� this� process,� the� Rx� MAC� performs� the� following� functions:�

�?� Detect� the� start� of� frame�

�?� Compare� the� MAC� address�

�?� Re-calculate� CRC�

�?� Process� the� control� frame� and� pass� it� to� the� flow� control� module.�

�The� Rx� MAC� operation� is� determined� by� programming� the� MODE� and� TX_RX_CTL� registers.� These� register� defini-�

�tions� and� bit� descriptions� can� be� found� in� Table� 2-4� on� page� 25� .� Note� that� setting� the� Gbit_en� bit� in� the� MODE� reg-�

�ister� to� high� sets� the� TSMAC� to� operate� in� 1G� mode� whereas� setting� the� Gbit_en� bit� to� low� sets� the� TSMAC� to�

�operate� in� 10/100� Mode.�

�IPUG51_03.0,� December� 2010�

�19�

�Tri-Speed� Ethernet� MAC� User’s� Guide�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

TS250-130F-2

POLYSWITCH PTC RESET 0.13A SMD

TS250-130F-B-0.5-2

POLYSWITCH PTC RESET 0.13A SMD

TS250-130F-RB-2

POLYSWITCH PTC RESET 0.13A SMD

TS250-130F-RC-2

POLYSWITCH PTC RESET 0.13A SMD

TS250-130F-RC-B-0.5-2

POLYSWITCH PTC RESET 0.13A SMD

TS600-170F-2

POLYSWITCH PTC RESET 0.17A T/R

TS600-200F-RA-B-0.5-2

POLYSWITCH PTC RESET 0.20A SMD

TS600-400F-2

POLYSWITCH PTC RESET 0.40A SMD

相关代理商/技术参数

TSMBG0505C

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|100V V(BO) MAX|DO-215AA

TSMBG0506C

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|110V V(BO) MAX|DO-214AA

TSMBG0507C

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|145V V(BO) MAX|DO-214AA

TSMBG0509C

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|185V V(BO) MAX|DO-215AA

TSMBG0510C

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|200V V(BO) MAX|DO-214AA

TSMBG0511C

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|210V V(BO) MAX|DO-214AA

TSMBG0512C

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|215V V(BO) MAX|DO-214AA

TSMBG0514C

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|250V V(BO) MAX|DO-214AA